# Secure Accelerator Design for Deep Neural Networks

by

# Lei Zhao

Master of Computer Science, Northwestern Polytechnical University, China, 2014

Submitted to the Graduate Faculty of the Department of Computer Science in partial fulfillment of the requirements for the degree of

**Doctor of Philosophy**

University of Pittsburgh

# UNIVERSITY OF PITTSBURGH DEPARTMENT OF COMPUTER SCIENCE

This dissertation was presented

by

Lei Zhao

It was defended on

April 8th 2022

and approved by

Dr. Youtao Zhang, Department of Computer Science, University of Pittsburgh

Dr. Adriana Kovashka, Department of Computer Science, University of Pittsburgh

Dr. Xulong Tang, Department of Computer Science, University of Pittsburgh

Dr. Jun Yang, Department of Electrical and Computer Engineering, University of

Pittsburgh

Copyright  $\bigcirc$  by Lei Zhao 2022

# Secure Accelerator Design for Deep Neural Networks

# Lei Zhao, PhD

## University of Pittsburgh, 2022

Deep neural networks (DNNs) have recently gained popularity in a wide range of modern application domains due to its superior inference accuracy. With growing problem size and complexity, modern DNNs, e.g., CNNs (convolutional neural networks), contain a large number of weights, which require tremendous efforts not only to prepare representative training data but also to train the network. There is an increasing demand to protect the DNN weights, an emerging intellectual property (IP) in the DNN field. This thesis proposes a line of solutions for protecting the DNN weights deployed on domain specific accelerators.

Firstly, I propose AEP, a DNN weights protection scheme for accelerators based on conventional CMOS based technologies. Because of the extremely high memory bandwidth demand in DNN accelerators, conventional encryption based approaches, which require the integration of expensive encryption engines, pose significant overheads on the execution latency and energy consumption. Instead, AEP enables effective IP protection by utilizing fingerprints generated from hardware characteristics to eliminate the need of encryption. Adopting such hardware fingerprints achieves high inference accuracy only on the authorized device, while unauthorized devices can not produce any useful results from the same set of weights.

Secondly, as the size of DNNs keeps increasing rapidly, the large number of intermediate results (i.e, the outputs from the previous layer and the inputs to the current layer) can not be held on-chip. These intermediate results also contain sensitive information about the DNN itself. In this part, I propose SCA which can securely off-load data dynamically generated inside the accelerator chip to off-chip memories. SCA is a full DNN protection scheme that protects both the DNN weights and the intermediate results, and supports both training and inference on CMOS based accelerators.

Thirdly, ReRAM based accelerators introduce new challenges to DNN IP protection due to their crossbar structure and non-volatility. ReRAM's non-volatility retains data even after the system is powered off, making the stored DNN weights vulnerable to attacks by simply reading out the ReRAM content. Because the crossbar structure can only compute on cleartext data, encrypting the ReRAM content is no longer a feasible solution in this scenario. To solve these issues, I propose SRA, a novel non-encryption base protection method that still maintains ReRAM's in-memory computing capability.

Lastly, although SRA provides security guarantees, the weights are represented in stochastic computing (SC) bit stream format, which induces a large storage overhead. However, conventional DNN model compression methods, such as pruning and quantization, are not applicable ReRAM based PIM accelerators. In this part, I propose BFlip — a novel DNN model compression scheme — to share crossbars among multiple bit matrices. BFlip not only reduces storage overhead but also improves performance and energy efficiency.

Keywords: neural network, security, accelerator, ReRAM, in-situ.

# **Table of Contents**

| Pre | face                   |                                                                           | xiii |

|-----|------------------------|---------------------------------------------------------------------------|------|

| 1.0 | IN                     | TRODUCTION                                                                | 1    |

|     | 1.1                    | Problem Statement                                                         | 2    |

|     | 1.2                    | Research Overview                                                         | 3    |

|     |                        | 1.2.1 Protect Weights with Hardware Fingerprints                          | 4    |

|     |                        | 1.2.2 Protect Weights and Intermediate Results with Hardware Fingerprints | 4    |

|     |                        | 1.2.3 DNN Protection for Non-Volatile PIM Accelerators                    | 5    |

|     |                        | 1.2.4 Model Compression for Non-Volatile PIM Accelerators                 | 6    |

|     | 1.3                    | Contributions                                                             | 7    |

|     | 1.4                    | Thesis Organization                                                       | 8    |

| 2.0 | $\mathbf{B}\mathbf{A}$ | CKGROUND                                                                  | 9    |

|     | 2.1                    | Deep Neural Networks                                                      | 9    |

|     |                        | 2.1.1 Convolutional Layers                                                | 10   |

|     |                        | 2.1.2 Classification Layers                                               | 10   |

|     |                        | 2.1.3 Activation Layers                                                   | 11   |

|     |                        | 2.1.4 Pooling Layers                                                      | 11   |

|     |                        | 2.1.5 Batch Normalization Layers                                          | 11   |

|     |                        | 2.1.6 Training vs. Inference                                              | 12   |

|     |                        | 2.1.7 Training with Approximation                                         | 13   |

|     | 2.2                    | DRAM/eDRAM                                                                | 14   |

|     | 2.3                    | ReRAM                                                                     | 17   |

|     |                        | 2.3.1 ReRAM Basics and PIM Computing                                      | 17   |

|     | 2.4                    | Stochastic Computing                                                      | 19   |

|     | 2.5                    | Related Work                                                              | 20   |

|     |                        | 2.5.1 Algorithm Validity                                                  | 20   |

|     |                        | 252 User Privacy                                                          | 21   |

|     |     | 2.5.3 Weight Confidentiality                           | 22 |

|-----|-----|--------------------------------------------------------|----|

| 3.0 | PR  | OTECT WEIGHTS USING HARDWARE FINGERPRINTS              | 24 |

|     | 3.1 | Threat Model                                           | 24 |

|     | 3.2 | Protection Scheme                                      | 25 |

|     |     | 3.2.1 Overview                                         | 25 |

|     |     | 3.2.2 Device Dependent Weight Matrices                 | 26 |

|     |     | 3.2.3 Device Dependent Error Masks                     | 29 |

|     |     | 3.2.4 Securing The Error Masks At The Client Side      | 31 |

|     | 3.3 | Accelerator Design                                     | 33 |

|     | 3.4 | Experimental Methodology                               | 34 |

|     | 3.5 | Results And Analysis                                   | 36 |

|     |     | 3.5.1 IP Protection Effectiveness                      | 36 |

|     |     | 3.5.2 Performance                                      | 36 |

|     |     | 3.5.3 Energy Consumption                               | 37 |

|     |     | 3.5.4 Training Overhead                                | 38 |

|     |     | 3.5.5 AEP Robustness                                   | 39 |

|     | 3.6 | Conclusion                                             | 40 |

| 4.0 | PR  | OTECT WEIGHTS AND INPUTS USING HARDWARE FINGER-        |    |

|     | PR  | INTS                                                   | 41 |

|     | 4.1 | Threat Model                                           | 42 |

|     | 4.2 | Protection Scheme                                      | 43 |

|     |     | 4.2.1 SC Based Protection                              | 44 |

|     |     | 4.2.1.1 Generating Device Dependent Bit Streams        | 44 |

|     |     | 4.2.1.2 Embedding Device Dependent Information in DNNs | 45 |

|     |     | 4.2.1.3 DNN Protection                                 | 46 |

|     |     | 4.2.2 Robust Protection                                | 47 |

|     |     | 4.2.3 Space-Optimized Stochastic Computing             | 48 |

|     | 4.3 | Accelerator Design                                     | 50 |

|     | 4.4 | Experimental Methodology                               | 51 |

|     | 15  | Regulte And Analysis                                   | 52 |

|               |                                                            | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|---------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                                                            | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 6.2.3 Flipping Bits in Bit Matrices                        | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 6.2.2 Clustering Bit Matrices                              | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 6.2.1 Decomposing Weight Matrices                          | 76                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.2           | Design Details                                             | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 6.1           | Overview                                                   | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\mathbf{RE}$ | DUCE SC STORAGE OVERHEAD IN RERAM CROSSBARS                | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.6           | Conclusion                                                 | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 5.5.4 Comparing with SFGE                                  | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 5.5.3 Energy                                               | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 5.5.2 Performance                                          | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 5.5.1 Protection                                           | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5           | Results And Analysis                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3           |                                                            | 66                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | V-                                                         | 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 0.2           |                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 57<br>58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16            |                                                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 54                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               |                                                            | 53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 4.5.1 Characteristics                                      | 52                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|               | 5.1<br>5.2<br>5.3<br>5.4<br>5.5<br>5.6<br><b>RE</b><br>6.1 | 4.5.2 Protection On Weights 4.5.3 Protection robustness in Training 4.5.4 Performance 4.5.5 Energy 4.5.6 Comparing with P³M 4.6 Conclusion  PROTECT WEIGHTS AND INPUTS IN RERAM CROSSBARS 5.1 Threat Model 5.2 Protection Scheme 5.2.1 Overview 5.2.2 Encrypted Crossbar Design 5.2.3 Bit Stream Mapping 5.2.4 SC Conversion 5.3 Accelerator Design 5.4 Experimental Methodology 5.5 Results And Analysis 5.5.1 Protection 5.5.2 Performance 5.5.3 Energy 5.5.4 Comparing with SFGE 5.6 Conclusion  REDUCE SC STORAGE OVERHEAD IN RERAM CROSSBARS 6.1 Overview 6.2 Design Details 6.2.1 Decomposing Weight Matrices 6.2.2 Clustering Bit Matrices |

|     |              | 6.2.6 Mapping to Crossbars   | 81 |

|-----|--------------|------------------------------|----|

|     |              | 6.2.7 Inference              | 83 |

|     | 6.3          | Accelerator Design           | 84 |

|     | 6.4          | Experimental Methodology     | 85 |

|     |              | 6.4.1 Accuracy Models        | 85 |

|     |              | 6.4.2 Hardware Models        | 86 |

|     | 6.5          | Results And Analysis         | 88 |

|     |              | 6.5.1 Accuracy               | 88 |

|     |              | 6.5.2 Performance and Energy | 90 |

|     | 6.6          | Conclusion                   | 91 |

| 7.0 | CO           | NCLUSION AND FUTURE WORK     | 93 |

|     | 7.1          | Summary                      | 93 |

|     | 7.2          | Future Research Directions   | 94 |

|     |              | 7.2.1 Algorithm Validity     | 94 |

|     |              | 7.2.2 User Privacy           | 95 |

| Rih | Ribliography |                              |    |

# List of Tables

| Table 1  | Inference Accuracy on Different Devices          | 29 |

|----------|--------------------------------------------------|----|

| Table 2  | Datasets and Networks                            | 34 |

| Table 3  | Simulator Setup                                  | 35 |

| Table 4  | Inference Accuracy with Different Error Masks    | 36 |

| Table 5  | DNN Pretection                                   | 47 |

| Table 6  | Datasets and Networks                            | 51 |

| Table 7  | SCA Characteristics                              | 52 |

| Table 8  | Inference Accuracy                               | 53 |

| Table 9  | SRA accelerator parameters                       | 67 |

| Table 10 | Benchmarks                                       | 68 |

| Table 11 | Inference Accuracy                               | 70 |

| Table 12 | Batch normalization's impact on accuracy         | 81 |

| Table 13 | Benchmarks                                       | 86 |

| Table 14 | BFlip accelerator parameters                     | 87 |

| Table 15 | Equivalent quantized bit width for different $m$ | 88 |

# List of Figures

| Figure 1  | The DNN training process                                                   | 12 |

|-----------|----------------------------------------------------------------------------|----|

| Figure 2  | The DNN training process with approximation                                | 13 |

| Figure 3  | DRAM/eDRAM organization                                                    | 14 |

| Figure 4  | eDRAM cell retention time distribution [2]                                 | 16 |

| Figure 5  | ReRAM and crossbar structure                                               | 17 |

| Figure 6  | 1T4R structure                                                             | 18 |

| Figure 7  | Stochastic Computing Implementation                                        | 19 |

| Figure 8  | The overview of AEP design                                                 | 26 |

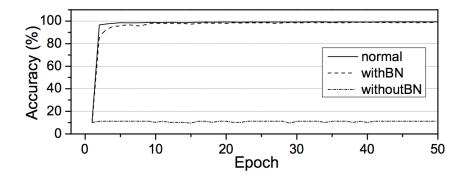

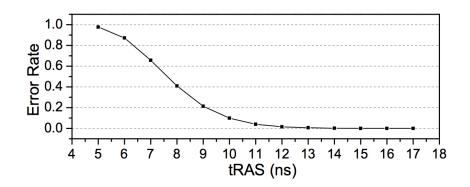

| Figure 9  | Training with and without batch normalization                              | 27 |

| Figure 10 | Reducing tras aggressively introduces memory errors                        | 30 |

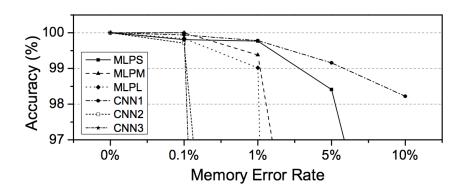

| Figure 11 | Different NNs have different error tolerance                               | 30 |

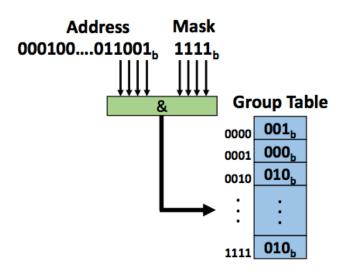

| Figure 12 | Dynamic tras adjustment                                                    | 32 |

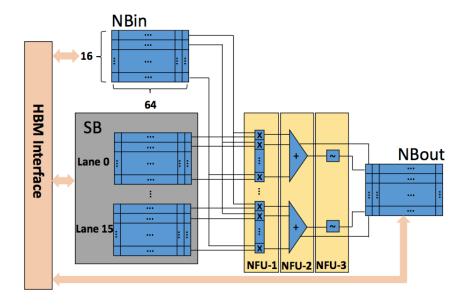

| Figure 13 | AEP accelerator                                                            | 33 |

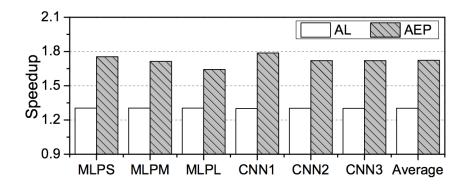

| Figure 14 | The performance comparison                                                 | 37 |

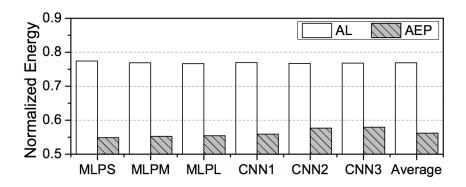

| Figure 15 | The energy consumption comparison                                          | 38 |

| Figure 16 | The server side training overhead.                                         | 38 |

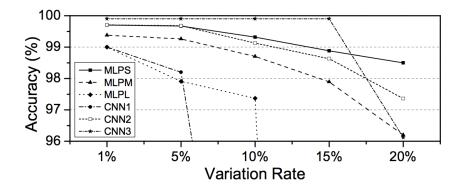

| Figure 17 | The AEP robustness.                                                        | 39 |

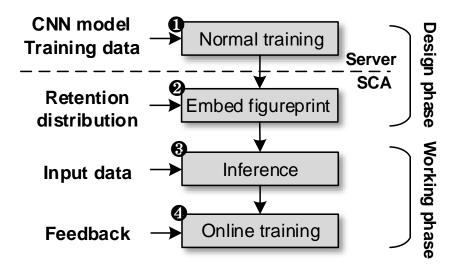

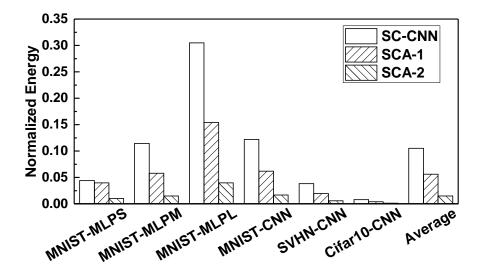

| Figure 18 | Overview of SCA's workflow                                                 | 43 |

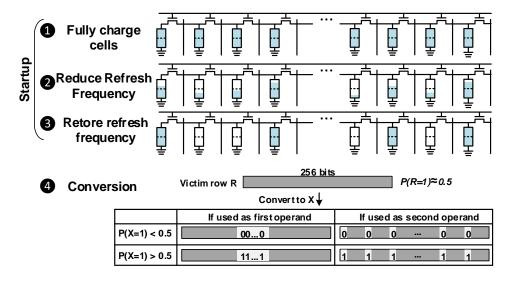

| Figure 19 | Stochastic computing conversion                                            | 44 |

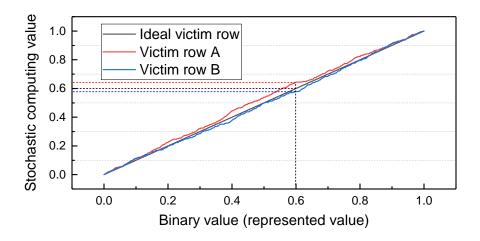

| Figure 20 | Stochastic computing values using different victim rows                    | 46 |

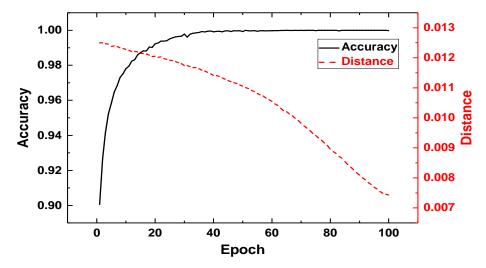

| Figure 21 | Accuracy and distance between weights of different formats for MNIST-MLPS. | 47 |

| Figure 22 | Convention and proposed SC Addition                                        | 49 |

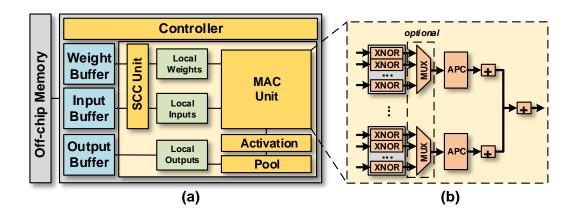

| Figure 23 | SCA accelerator                                                            | 50 |

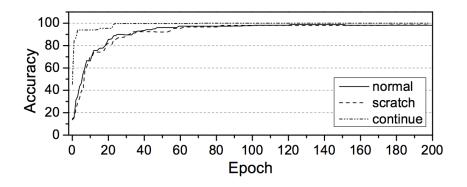

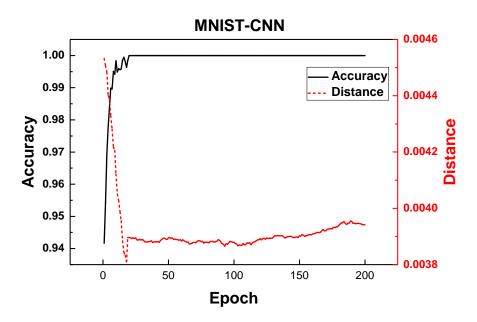

| Figure 24 | Protection robustness in training                                          | 54 |

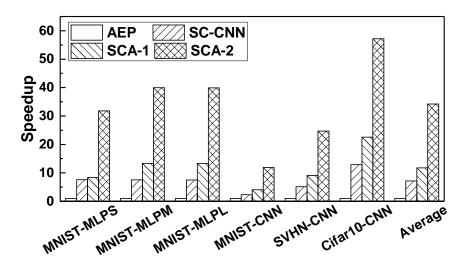

| Figure 25 | Speedup.                                                                   | 55 |

| Figure 26 | Normalized energy consumption                                              | 56 |

| Figure 27 | An overview of the SRA workflow                                          | 60 |

|-----------|--------------------------------------------------------------------------|----|

| Figure 28 | The rotated layout of the 1T4R structure                                 | 61 |

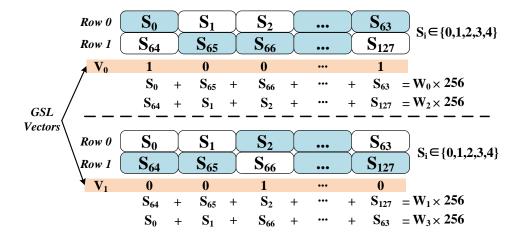

| Figure 29 | Mapping 4 weights on two rows in the crossbar                            | 62 |

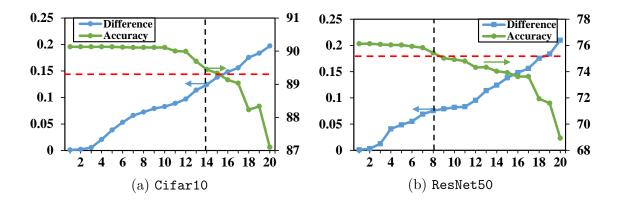

| Figure 30 | Tolerance of $n$ for Cifar10 and ResNet50                                | 64 |

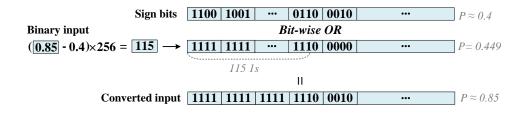

| Figure 31 | An example of converting 0.85 from binary format to SC format            | 65 |

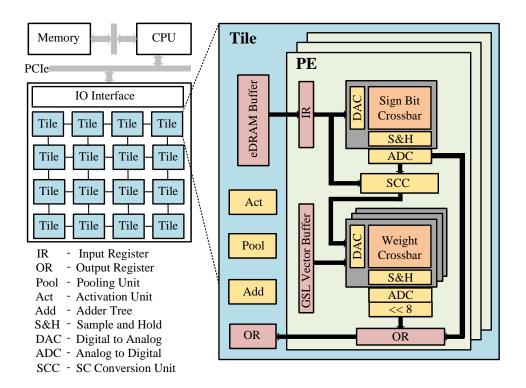

| Figure 32 | SRA accelerator                                                          | 66 |

| Figure 33 | Accuracy with increasing number of $\mathit{GSL}$ vectors                | 69 |

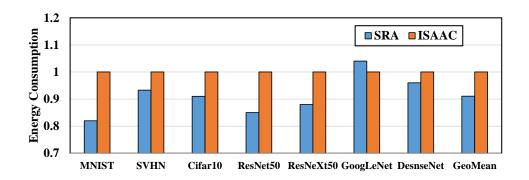

| Figure 34 | Speedup of SRA over ISAAC                                                | 70 |

| Figure 35 | Energy consumption of SRA over ISAAC                                     | 71 |

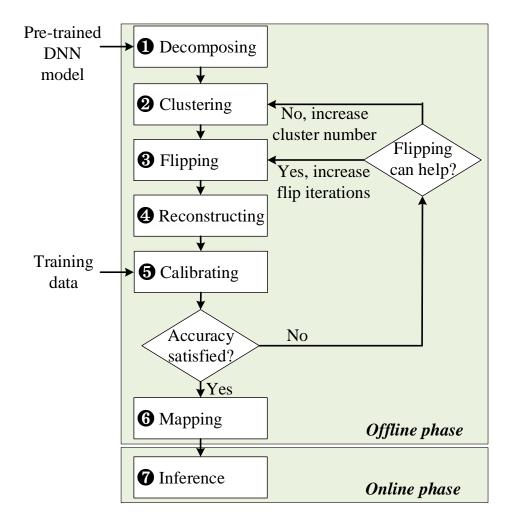

| Figure 36 | The overview of BFlip's workflow                                         | 75 |

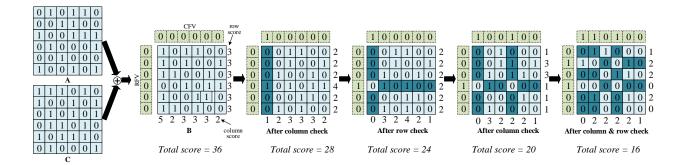

| Figure 37 | Example of flipping rows and columns to minimize two matrices' distance. | 77 |

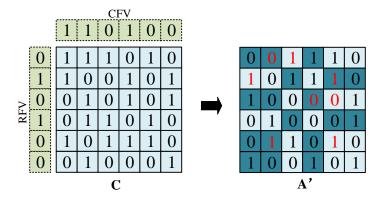

| Figure 38 | Reconstruct A' from C                                                    | 80 |

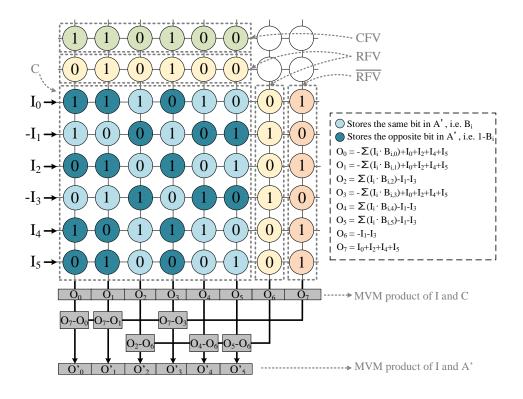

| Figure 39 | Map centroid bit matrix and meta data to crossbar                        | 82 |

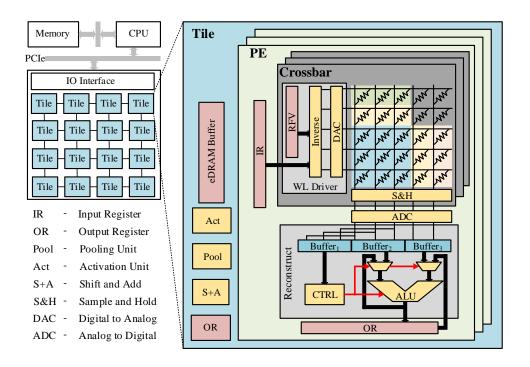

| Figure 40 | BFlip accelerator                                                        | 84 |

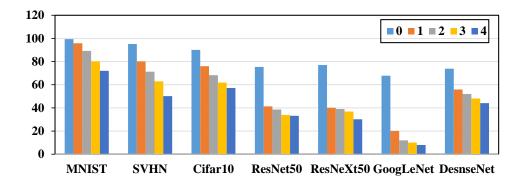

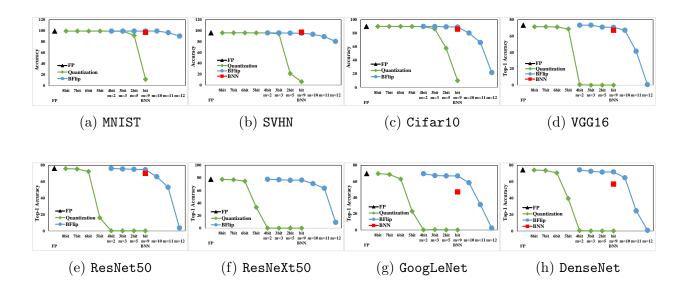

| Figure 41 | Accuracy of the full-precision baseline, quantization, BNN and BFlip     | 89 |

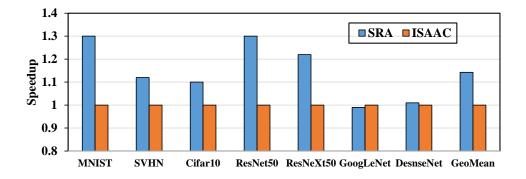

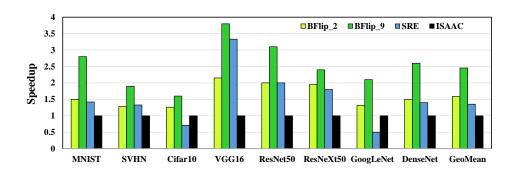

| Figure 42 | Speedup of BFlip over baselines                                          | 90 |

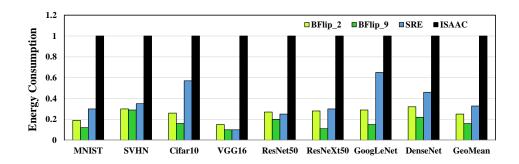

| Figure 43 | Energy consumption of BFlip over baselines                               | 91 |

#### **Preface**

I would like to thank all the people that I have met and worked with during my Ph.D study. First and foremost, I would like to thank my advisor, Professor Youtao Zhang, for his endless support. During the Ph.D program, he has put tremendous amount of effort to guide me through each step to explore and research. I am also grateful for the helps from Professor Jun Yang and Professor Xulong Tang for their comments and valuable advice on my research and presentations in our periodic lab-wise meeting. They taught me lots of things about doing research, and constantly provided insightful discussions and feedbacks on on my research projects and conference presentations.

Sincere thanks to all the committee members: Professor Youtao Zhang, Professor Jun Yang, Professor Adriana Kovashka and Professor Xulong Tang, for their time, efforts and valuable inputs into both the thesis proposal and final dissertation. Without their great helps, this dissertation would not be possible.

Thanks to all the colleagues in Professor Zhang's lab. The interesting and enjoyable discussions helped a lot in my research works. I had a great time with them for the past few years both inside and outside research.

Finally, I take this opportunity to express my gratitute to my family for their love, unfailing encouragement and support.

#### 1.0 INTRODUCTION

Deep Neural Networks (DNNs) are machine learning approaches that, by exploiting the rapidly increasing computation power of modern computers, achieve superior inference accuracy improvements over traditional machine learning algorithms. Therefore, DNNs are gaining popularity in a wide range of modern application domains, e.g., computer vision [21] and speech recognition [32].

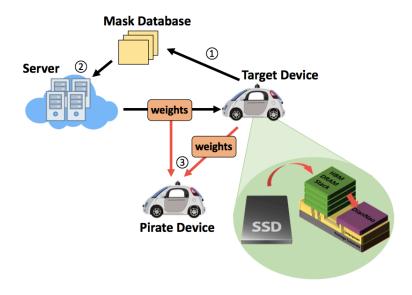

A typical DNN is composed of its layer structure as well as the massive amount of weights in each layer. While the layer structure is usually well known (i.e., the layers of a DNN are from a small set of common layer types), the weight values are more problem dependent and require not only a large number of computing iterations to train but also the efforts to prepare the effective training datasets which may include sensitive and/or proprietary data. Therefore, the DNN (especially the trained weights) is an intellectual property (IP) that needs to be protected. Leaking such information will result in huge losses. On the one hand, adversaries may abuse the DNN without getting permission. For example, the object tracking and recognition DNN of an autonomous driving car may be pirated, which speeds up the development of new systems from the competitors. On the other hand, adversaries may perform security attacks on the weights, such as changing the output of a DNN by adversarial examples.

Within each layer, the computations on the weights are highly parallelizable. The intrinsic memory and computation intensity of DNNs has driven the development of hardware accelerators for high performance and energy efficiency. For example, the DianNao accelerator [14] achieves 118× performance speedup and 21× energy reduction over an SIMD CPU. However, the massive amount of memory access remains a major bottleneck for hardware DNN accelerators, as concluded in [14]. This poses a challenge in using the conventional encryption based methods to protect DNNs that are deployed on accelerators. There is a huge demand for developing new efficient IP protection schemes for DNN accelerators.

#### 1.1 Problem Statement

For the DNNs that are deployed on the client side, it is challenging to design effective protection solutions. A naive solution to protect DNNs is to use encryption. To convoy the weights to the accelerator without being exposed to the third party during the process, we may adopt the XOM design [50] and the privacy enhancement [82]. It works briefly as follows. We first upgrade the accelerator with a small TCB (trusted computing base) that contains a crypto engine and PKI (public key infrastructure) support, i.e., the private key is kept secret while the public key is released to the end users and servers. The server encrypts the weights using a session key and then encrypts the session key with the public key of the accelerator. Thus, only the target accelerator can decrypt the session key and then decrypt the encrypted weights before computation.

Unfortunately, this simple solution faces severe scalability issues. Given that DNNs are increasingly adopted to accomplish challenging tasks in various application domains, their sizes, i.e., the number of weights in the network, grow rapidly. For example, Le et al. [43] created a DNN with 1 billion weight parameters, Catanzaro et al. [18] used a DNN that has 11 billion parameters. More recently, Ni et al. [57] built a DNN that contains over 15 billion parameters, which requires more than 30GB if using 16-bit fixed point. It consists of two convolutional layers and one classifier layer, which have 3GB, 18GB, and 12GB weights, respectively.

A DNN accelerator, due to its limited on-chip memory, needs to load and decrypt a large number of weights when starting a new layer. Adopting High Bandwidth Memory (HBM) improves the maximal bandwidth but not the decryption latency. For example, without encrypting and decrypting the weights, the second layer of the above DNN [57] finishes in  $504\mu$ s using DianNao. However, even we optimistically assume that the weights of the third layer (i.e., 12GB) can be loaded in parallel with the execution of the second layer, decrypting the weights with a fully-unrolled, pipelined AES implementation needs 349ms [3]. Here we optimistically assume the AES decryption engine consists of multiple copies such that it can match the peak HBM bandwidth, i.e., 256GB/s. The weight decryption can easily become the latency bottleneck of the whole system.

In addition, the encryption based scheme is not applicable to process-in-memory (PIM) accelerators. For example, ReRAM based accelerators store the DNN weights as the resistance of ReRAM cells which are organized in a crossbar structure, while the inputs are fed into the crossbar in the form of voltage levels. The matrix vector multiplication (MVM) is performed based on Kirchoff's Law, i.e., the current flowing out represents the MVM results. This computation paradigm can only compute on cleartext data.

Therefore, the encryption based scheme is less preferred and we need to find another more efficient way to provide effective DNN weights protection.

#### 1.2 Research Overview

Our research aims to achieve the following goals: (i) protect the embedded DNNs with little or no computation overhead; (ii) guarantee the security of the deployed DNN inside the accelerators; (iii) support accelerators based on a variety of technologies.

To achieve the above goals, in this thesis we propose a series of hardware based DNN protection schemes on accelerators. Firstly, we propose to utilize the intrinsic hardware characteristics to protect the embedded DNNs, thus avoiding the expensive encryption and decryption operations. Secondly, our proposed schemes hide the actual weights that are used in computation after loading onto the accelerators. Even if the host CPU and/or off-chip memory are compromised, the security of the DNNs can still be guaranteed during execution. Lastly, we extend our schemes onto non-volatile in-situ accelerators. Since in-situ computing can only operate on cleartext data, we propose a novel shuffle based protection scheme to maintain the in-situ computing capabilities. To tackle the storage and computing overheads in the shuffle based protection scheme, we also propose novel model compression schemes for ReRAM accelerators.

# 1.2.1 Protect Weights with Hardware Fingerprints

DNNs are usually over-parameterized, which makes them tolerant to errors in the computing data as well as the computation itself. At the same time, DNNs usually find local minima on the loss surface as their solution. Given these two characteristics, we observe that if we first train the DNN with stuck errors at some fixed positions in the DNN weights (i.e., making the corresponding bits of the data stuck at 0 or 1 during the entire training process), the trained DNN can still produce high accurate predictions on classification tasks. However, if we manually flip the previously stuck bits in the trained weights (i.e., change the bit to 1 if it was stuck at 0 during training, change the bit to 0 if it was stuck at 1 during training), the modified DNN will significantly reduce its prediction accuracy, making the DNN unusable.

From the above observation, we utilize this phenomenon to restrict the DNN on a specific hardware [83]. Specifically, we extract the error distribution in the memory of a specific device. It has been reported that the DRAM timing induced errors follow a fixed spatial distribution, but change across different individual devices [2]. This error distribution can be used as the unique fingerprint for this device. We then train the DNN with these errors statically present in the weights to get a well-functioning DNN. Before deploying the DNN on the device, we manually flip the previous error bits to make the DNN a malfunctioning one. During run-time, the device uses the same DRAM timing to generate errors, thus automatically flipping the errors bits back to make the DNN well-functioning again.

The well-functioning weights only exist during run-time after they are loaded into the DRAM. This makes the DNN weights stored outside the DRAM and accelerator useless to the adversaries, thus effectively protecting the DNN IP. At the same time, the reduced DRAM timing can also bring performance and energy improvements.

# 1.2.2 Protect Weights and Intermediate Results with Hardware Fingerprints

Many DNNs demand post-deployment training, i.e., there is a need to train the deployed DNNs to achieve improved inference accuracy. It is usually not preferable to send the edge devices to the manufacturer for further training. There are two reasons: (i) Post-deployment

training may take advantage of end users' private data, which creates privacy concerns if sending such data back to the device manufacturer; (ii) it is often physically difficult to retrieve the devices and send to the manufacturer. Unfortunately, existing IP protection schemes focus mainly on the inference phase and lack the ability to be extended to the training phase. For example, in our first scheme described above, we need to know the DRAM error distribution of each device to train a device-dependent DNN. However, the error distribution can only be implicitly applied to the weights by reducing the DRAM timing but is not explicitly visible to the end devices. This prevents the devices to generate the malfunctioning DNN after the weights got updated.

We have the new observation that the precision difference between Stochastic Computing (SC) format and binary format representations can also be used as fingerprints to protect DNN IPs [84]. Weights are stored in binary format outside the accelerator. When they are loaded into the accelerator, the weights will be converted into SC format with some precision errors. We use the same training method as in the previous scheme, but this time we use the precision errors instead. To make the precision error distribution also device dependent, we propose a novel binary to SC conversion method which transforms DRAM errors into the precision error.

This is the first scheme that supports IP protection for both training and inference on accelerators. At the same time, our optimized computing paradigm in SC domain also provides improvements in performance and energy consumption.

#### 1.2.3 DNN Protection for Non-Volatile PIM Accelerators

As non-volatile PIM accelerators could provide higher computation parallelism and avoid massive data movement between the memory and computing unit, ReRAM is a good fit for DNN computing. However, how to protect the DNN IPs after their deployment on ReRAM accelerators remains a less addressed problem. Compared to CMOS accelerators, new challenges arise: i) ReRAM's non-volatility retains data after power is off, making the stored weights easier to be extracted out from the accelerator; ii) ReRAM's crossbar structure can only compute on cleartext data, making encryption on weights impossible.

We utilize the new 1T4R structure [79] together with SC to protect DNN weights on ReRAM crossbars [86]. The multiplication is performed in the SC format, and all weights and inputs are represented in the form of bit streams. With the 1T4R structure, the long bits stream of each weight can be truncated into multiple slices. During run time, the slices will be dynamically combined to reconstruct the bit stream for computing. Therefore, even if the adversary extracts all the content from the crossbars, the actual reconstructed bit streams are still hidden without knowing the recombine pattern. Only the recombine pattern needs to be stored as confidential information. Using these shuffled slices for protection also avoids the need for encryption, and still maintains the PIM capability of ReRAM.

Another contribution of this design is to reuse the same slices with different recombine patterns. This can be regarded as a model compression technique, which significantly reduces the model size after being deployed onto the ReRAM crossbars.

# 1.2.4 Model Compression for Non-Volatile PIM Accelerators

On the one hand, although ReRAM is denser than traditional SRAM and DRAM, it still faces the pressure of rapidly increasing DNN weight sizes. On the other hand, because of ReRAM's low endurance and slow write speed, existing ReRAM based DNN accelerators require weights to be statically mapped on the crossbars to avoid frequently programming the cells. All these issues require a large number of crossbars which increases the hardware cost of ReRAM based accelerator products, or demands model compression techniques to utilize the limited resources more efficiently.

Unfortunately, existing model compression methods (e.g., weight pruning [54] or weight quantization [35]) that exploit weight sparsity and weight redundancy can not be effectively applied to ReRAM based DNN accelerators. Pruning removes the weights whose values are close to zero. However, because ReRAM crossbar is a tightly coupled structure, exploiting the random and irregular distribution of zero weights requires complex control and peripheral circuits. Quantization uses a shorter bit width to represent weight values, e.g., using 8-bit fixed point instead of 32-bit floating point. However, bit width below eight usually incurs significant accuracy degradation [37, 40].

In addition to the model compression technique in our previous scheme discussed above, we propose a second model compression technique that could be applied on ReRAM based accelerators [85]. We flip the bits in crossbars so that multiple bit matrices can share the same crossbar. Because the bits in a crossbar are accessed uniformly, separately flipping each bit induces large metadata and complex control logic. Therefore, we propose to only flip the bits in the granularity of rows and/or columns in a crossbar. We first cluster similar bit matrices together and then flip them to match the cluster's centroid bit matrix. For each cluster, only the centroid bit matrix is stored in the accelerator while all other bit matrices will be reconstructed from the centroid bit matrix during inference. However, since the bits can only be flipped in the granularity of rows and columns, it is very likely that a bit matrix cannot be flipped to perfectly match the centroid bit matrix. We apply a post-flipping calibration method that only updates the distribution statistics of batch normalization layers to mitigate the precision loss.

#### 1.3 Contributions

This thesis makes the following contributions:

- DNN related security issues have been widely studied in both research and industry. However, most of them focus on the robustness of the DNN's accuracy, while the security of DNN IP is less addressed. Instead, we provide a thorough investigation of this overlooked yet important issue and propose effective solutions.

- We propose a series of solutions that target various security requirements and different types of accelerators. Specifically, we propose the solutions based on the order of their threat model's restrictions, i.e., from the assumptions that the adversaries only have non-expert attack capabilities all the way to the scenarios with the strongest attacks. In this way, the users can choose different solutions according to their specific security requirements.

- Going further, we also extend the protection on accelerators that are based on emerging memory technologies. Because ReRAM's PIM computing can only operate on cleartext

data, existing encryption based protection methods are no longer applicable to protect weights stored in ReRAM crossbars. This thesis proposes the first DNN IP protection scheme that can be used in ReRAM PIM accelerators.

Model compression is an important topic to make DNNs practical on resource constrained

accelerators. However, ReRAM's crossbar is a tightly coupled structure, most state-ofthe-art model compression methods can not be used in ReRAM accelerators. This thesis

proposes two novel model compression schemes to fill this gap.

# 1.4 Thesis Organization

The rest of this thesis is organized as follows: Chapter 2 introduces the background knowledge used in the proposed designs. This chapter also presents related work on securing DNN IPs on accelerators. Chapter 3 describes the details of our first design (AEP), which protects DNN weights using hardware fingerprints. Chapter 4 presents our second design (SCA) – a more general solution that protects both DNN weights and intermediate results, and supports both training and inference. Chapter 5 describes our third design (SRA) that could protect the weights in SC format for ReRAM based accelerators. (SRA) also comes with a new model compression method that could effectively reduce the number of crossbars to store the deployed weights. To further reduce the resource demand on ReRAM based accelerators, Chapter 6 proposes another more general model compression method that does not require the weights to be in SC format.

#### 2.0 BACKGROUND

In this chapter, we introduce some preliminary backgrounds that could help to understand our proposed protection schemes in later chapters. Section 2.1 introduces the basic concept of DNNs and the most common layers that are present in DNNs. Section 2.2 describes the DRAM/eDRAM structure which is the base memory technology in our AEP and SCA designs. Section 2.3 describes one type of the emerging non-volatile memories — ReRAM structure — which servers as the base memory technology of our SRA design. Section 2.4 gives the introduction of the Stochastic Computing technique which is utilized in our SCA and SRA designs to produce hardware fingerprints. Finally in the last part of this chapter, we also provide a brief literature review that are related to our work in Section 2.5.

## 2.1 Deep Neural Networks

A Deep Neural Network (DNN) is a layered structure that contains multiple layers of neurons. The outputs of one layer's neurons are used as the inputs to the following layer (except the last layer whose outputs are the DNN's outputs). The outputs of one layer are used as inputs to its next layer in the network structure. Therefore, these dynamically produced data between layers are also called intermediate results in this thesis.

A DNN layer can be one of various types. The most common used types are: convolutional layers, classifier layers, activation layers, pooling layers and batch normalization layers. If a DNN contains convolutional layers, it is also usually called Convolutional Neural Networks (CNNs). Since CNNs are the most popular DNNs and convolutional layers take the majority of computation time, we mainly target at CNNs in this thesis.

# 2.1.1 Convolutional Layers

The weights in a convolutional layer are composed of multiple 3-dimensional filters and a 1-dimensional vector. All the filters are organized as a 4-dimensional tensor  $(K \times C \times R \times S)$ . K is the number of 3-dimensional filters. Each filter has C channels, each channel is a  $R \times S$  matrix. Each filter has its corresponding bias (a scalar value). So, all the biases are organized as a 1-dimensional vector of length K.

The inputs to a convolutional layer are organized as a 4-dimensional tensor  $(N \times C \times H \times W)$ . N is the number of inputs (also called batch size). C is the number of channels of one input, each channel is a  $H \times W$  matrix.

The convolution is computed by sliding each filter over the H and W dimensions on the inputs. Each convolution step performs a multiply–accumulate operation (MAC) between the filter weights and the overlapped inputs to produce a single value, which will then add the bias of that filter to generate one output value, as shown in Equation 1.  $\mathbf{O}$ ,  $\mathbf{F}$ ,  $\mathbf{I}$  and  $\mathbf{b}$  are the output tensor, filter tensor, input tensor, and bias vector, respectively. All the outputs are also organized as a 4- dimensional tensor  $(N \times K \times E \times F)$ . N is the number of outputs. Since the results produced by the same filter are put in the same channel in the outputs, the number of output channels is K, i.e., the same as the number of filters. E and F are the height and width of one output channel.

$$\mathbf{O}[n, k, e, f] = \sum_{c=0}^{C-1} \sum_{r=0}^{R-1} \sum_{s=0}^{S-1} \mathbf{F}[k, r, s] \mathbf{I}[h + r, w + s] + \mathbf{b}[k]$$

$$0 \le n < N, 0 \le k < K, 0 \le c < C, 0 \le h < H, 0 \le w < W, 0 \le e < E, 0 \le f < F$$

(1)

#### 2.1.2 Classification Layers

A classification layer is named so because its purpose is to perform the classification task based on the features learned by previous layers. They are often located at the end of the layer structure. A classification layer also computes Equation 1, and can be viewed as a special case of convolutional layers. We can use the same notifications of convolutional layers. Each input is a 2-dimensional matrix, i.e.,  $\mathbf{I}^{N \times C \times 1 \times 1}$ . Each output is also a 2-dimensional

vector i.e.,  $\mathbf{O}^{N \times K \times 1 \times 1}$ . There is a full connection with the inputs and outputs, i.e.,  $\mathbf{F}^{K \times 1 \times 1}$  and  $\mathbf{b}^{K}$ . Therefore, classification layers are also called fully connected layers.

# 2.1.3 Activation Layers

A DNN containing only convolutional layers and classification layers are still a linear model as all the computations are additions and multiplications. To solve more complex problems, the activation layers are used to introduce nonlinearity. An activation layer applies a nonlinear function, e.g., ReLU (max(0,x)), Sigmoid  $(\frac{1}{1+e^{-x}})$ , on each input value separately. So an activation layer is an element-wise operation and does not change the dimensions of the inputs.

# 2.1.4 Pooling Layers

Similar to convolutional layers, a pooling layer slides a filter along the width and height of its inputs. However, each filter is two dimensional (i.e., C = 1) so that it applies the filter on each channel of the inputs separately. Another difference is that there are no weights in a pooling layer's filter, it only computes the max or average over the covered input values.

#### 2.1.5 Batch Normalization Layers

Batch normalization layers normalizes the inputs into a standard normal distribution by applying Equation 2.

$$y = \frac{x - \mu}{\sqrt{\sigma^2 + \epsilon}} \gamma + \beta \tag{2}$$

x is each single input value to this batch normalization layer. ( $\mu$ ) and ( $\sigma$ ) are the mean and standard deviation computed from all the input values in the current channel.  $\gamma$  and  $\beta$  are two learnable parameters like the weights in convolutional and classifier layers.  $\epsilon$  is a small constant defined prior the training. After applying Equation 2, the distribution of each output channel is normally distributed.

# 2.1.6 Training vs. Inference

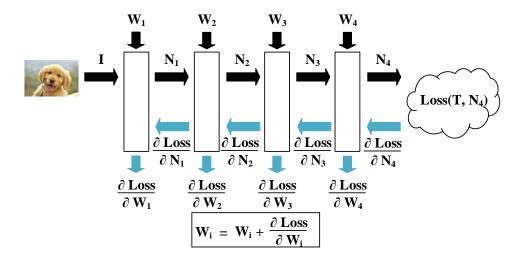

Figure 1: The DNN training process.

A DNN has two different computing phases: training and inference. The training phase is to adjust the trainable weights of convolutional layers, classification layers and batch normalization layers to make the DNN fit a specific function. Then the trained weights are used in the inference phase to perform tasks, such as image classification, speech recognition, etc. Figure 1 shows the training process in an example 4-layer DNN that classifies images. The black arrows show the forward propagation pass. The first layer takes the image as inputs I together with this layer's weights  $W_1$  to calculate the outputs  $N_1$ , which are then fed into the next layer. After the last layer computes its outputs  $N_4$ , the Loss function calculates the difference between the network's outputs and the groundtruth T. Then the loss goes back through the network layer by layer in the backward propagation pass, denoted by the blue arrows. Take the last layer as an example, the inputs to this layer in the backward propagation pass are the gradients w.r.t.  $N_4$ . This layer computes the gradients w.r.t. its weights (i.e.,  $\frac{\partial Loss}{\partial W_4}$ ) as well as the inputs to this layer in the forward propagation pass (i.e.,  $\frac{\partial Loss}{\partial N_3}$ ). After all the layers finishes the backward propagation pass, each layer's weights will be updated by applying the equation  $W_i = W_i - \eta \frac{\partial Loss}{\partial W_i}$  (1 \le i \le 4), where  $\eta$  is the learning rate. The training phase is an iterative process, i.e., multiple rounds of forward propagation pass and backward propagation pass, until the loss stops decreasing.

Once the training phase is over, all the weights will be frozen. The inference phase uses the weights trained in the training phase, and only executes the forward propagation pass to classify an input image. The output of the last layer  $(N_4)$  is the predicted label of the input image.

# 2.1.7 Training with Approximation

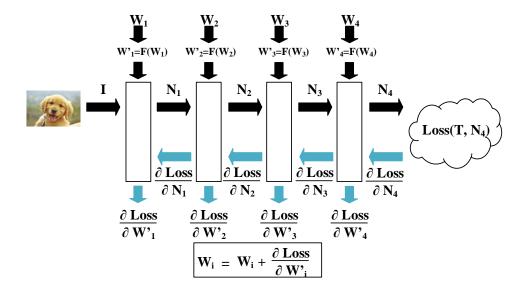

Figure 2: The DNN training process with approximation.

It has been proven that full precision computation (32/64-bit floating point) is not necessary in DNNs [29, 39]. Most hardware accelerators use fixed point representation for weights and/or inputs [14, 15]. Chen et al. [14] used different fixed point widths to train and inference DNNs. They found 16-bit fixed point is sufficient in inference phase, however, in order to make the training phase converge, at least 32-bit fixed point should be used in training. Courbariaux et al. [19] also investigated different low precision operations in training DNNs. They can achieve negligible accuracy loss with lower precision fixed point computations. Courbariaux et al. [20] then proposed to use binary weights (only 1 bit) in inference. The proposed training process in their work is shown in Figure 2. They keep two sets of weights, one is the full precision floating point version  $W_i$ , the other one is the low precision fixed

point weights  $W'_i$ . They first binarize the weights through function F:

$$W'_{i} = F(W_{i}) = sign(W_{i}), (1 \le i \le 4)$$

and use  $W'_i$  in the forward propagation pass. During the backward propagation pass, they calculate the gradients w.r.t.  $W'_i$ , but only use the gradients to update the full precision weights  $W_i$ . In inference phase, only  $W'_i$  are used, so the floating point weights  $W_i$  can be discarded. This binarized DNN incurs some accuracy drops compared with the full precision DNN, but significantly reduces the storage requirement, memory bandwidth demand, and the computation involved as multiplications can be completely eliminated.

# 2.2 DRAM/eDRAM

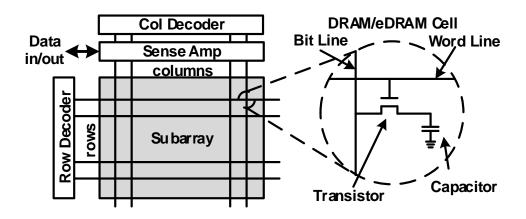

Figure 3: DRAM/eDRAM organization.

Dynamic random access memory (DRAM) is the most widely used type of memory in computer systems. Embedded DRAM (eDRAM) is the type of DRAM that is integrated on the same die of other computation logics (e.g., CPUs). DRAM and eDRAM have the similar structure, which is shown in Figure 3. The right part of Figure 3 shows the structure of one DRAM/eDRAM cell. A cell stores 1 bit data according to the amount of charge in the capacitor. The transistor controls the capacitor's connection with the bit line. During

a read/write operations, the transistor connects the capacitor with the bit line, so that the charges stored in the capacitor can be shared with the bit line. Specifically, in a read operation, the bit line is first precharged to half of the predefined voltage, i.e.,  $\frac{V_t}{2}$ . According to whether the cell contains charges, when the transistor connects the bit line and the cell, the bit line voltage will be raised up or dropped down because of charge sharing. Then the sense amplifier will detect the minor change on the bit line voltage to determine the value stored in the cell. As we can see, the read operation is destructive, i.e., the value stored in the cell is modified by the read operation. Therefore, a restore operation (similar to a write operation) is needed to write the original value back to the cell. In a write operation, the bit line is first programmed to  $V_t$  or 0. When the transistor connects the bit line and the cell, the value in the cell will be overwritten because the capacitance of the bit line is much larger than that of the cell.

The cells are organized as rectangular subarrays, consisting of rows and columns (left part of Figure 3). To access data in the subarray, the address first sends a subset of its bits (called the row address) to the row decoder, which will select an entire row from the subarray. The selected row will be read out and holded in the sense amplifier. Then another subset of the address bits (called the column address) is sent to the column decoder to select the target bits from the sense amplifier.

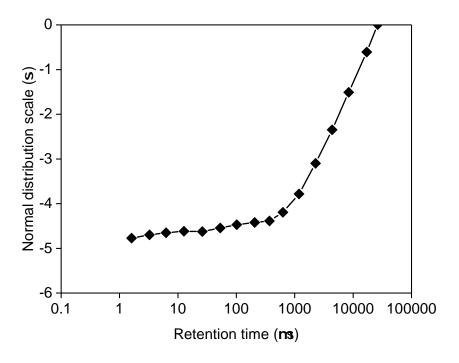

Figure 4: eDRAM cell retention time distribution [2].

Due to process variations, different DRAM/eDRAM cells leak charge at different speeds. The determining factors includes the size of the capacitor, gate length of the transistor, etc. It is impossible to make all these parameters exactly the for all the cells on a device. Usually, DRAM/eDRAM manufacturers follows the same timing standard to make their product compatible with each other. The standard (also known as JEDEC [1]) defines a set of conservative timings to guard the success of the operations. Violating the timing standard may induce data errors on the device. For example, recent studies showed that the bit error rates increase with reduced refresh frequency [2], as shown in Figure 4. Because weak cells leak charge much faster and the distribution of these weak cells are device dependent, many prior works [49, 17] have exploited it to device physical unclonable functions (PUFs) that map a set of input parameters to unique, device-specific signatures that can be generated repeatably and reliably.

#### 2.3 ReRAM

# 2.3.1 ReRAM Basics and PIM Computing

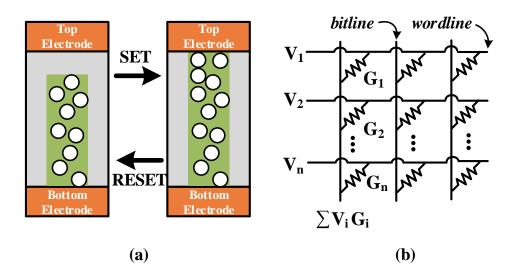

Figure 5: ReRAM and crossbar structure.

A ReRAM cell is a three-layer structure, consisting of a resistive switching layer sand-wiched between the top and bottom electrodes, as shown in Figure 5(a). The information stored in a cell is determined by the resistance between the two electrodes. The cell's resistance can be programmed by *SET* and *RESET* operations to change the oxygen vacancy filament connecting the two electrodes. The oxygen vacancy filament determines the resistance between the two electrodes. Usually, a cell in the high resistance state stores 1, while a cell in low resistance state store 0. It is also possible to store more than 1 bit in a single ReRAM cell by dividing the resistance range into multiple levels to achieve higher density. However, this requires more complex I/O circuits and poses a challenge to programming accuracy. Therefore, many works [7, 85] use single-bit cells in PIM designs for practical concerns.

ReRAM cells can be organized in a compact crossbar structure to achieve the smallest  $4F^2$  cell size. Figure 5(b) shows the matrix vector multiplication (MVM) operations taking place in a crossbar. The conductance (i.e., the reciprocal of the resistance) of the ReRAM

cells are programmed according to the values in a matrix. The voltages of the word lines represents the values of a vector. Thus, the current flowing out from each bit line conveys the MVM result. This crossbar structure is an excellent match for DNN computing, whose core computation is MVM. The DNN weights are stored in the cells, while the input vector is converted into word line voltages. Compared to traditional Von Neumann architecture, the computation takes place inside the crossbar, avoiding the need to move the weight matrices for computation.

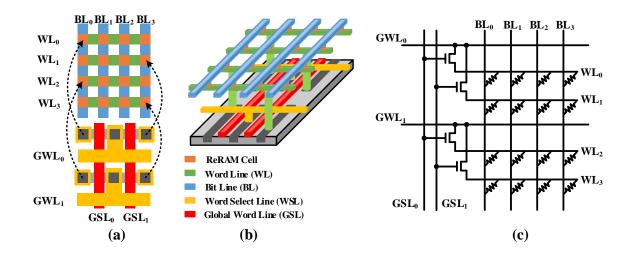

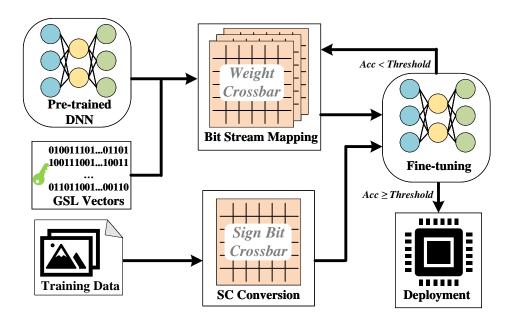

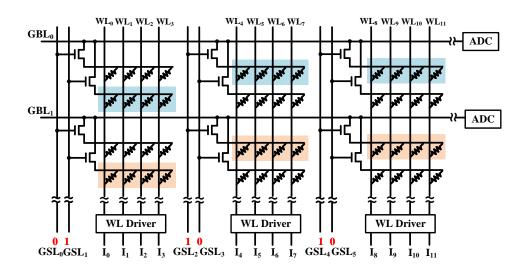

Figure 6: 1T4R structure.

Because there are no access transistors to isolate adjacent cells, unactivated word lines or bit lines can induce leakage current (called *sneak current*) during access. Recently, [79] presented a 1T4R ReRAM crossbar structure to address the sneak current problem. In a 1T4R crossbar, each  $4 \times 4$  sub-array is isolated from other cells in the crossbar by 4 dedicated transistors, which are fabricated underneath the sub-array. Figure 6(a) and (b) illustrate the 2D and 3D layout, respectively. [79] fabricated a 1T4R test chip to show that the 4 transistors can be fully hidden underneath the area of the  $4 \times 4$  ReRAM sub-array, thus still achieving the  $4F^2$  cell size. Figure 6(c) shows the schematic diagram of one  $4 \times 4$  sub-array. Besides bit lines (BLs) and word lines (WLs), there are also two global select lines (GSLs)

and two global word lines (GWLs). The GSLs are used to select which rows in the sub-array to access. The GWLs connect to other sub-arrays horizontally in the crossbar.

# 2.4 Stochastic Computing

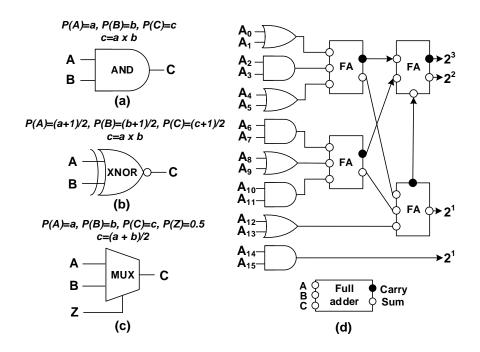

Figure 7: Stochastic Computing Implementation.

Stochastic Computing (SC) represents a number by using a random bit steam, in which the probability of the appearance of 1s indicates the represented value. For example, the bit stream X = 011001001 represents 0.4 because the probability P(X = 1) = 0.4. Since values are represented by probabilities, the representation for a value is not unique. A multiplication between two SC numbers can be implemented using bit-wise AND operations, as shown in Figure 7(a). However, only values in the range [0,1] can be encoded using the above method (called unipolar format). The bipolar format can represent values in the range [-1,1] by scaling it in [0,1]. For example, the value  $x = -0.4 \in [-1,1]$  is first scaled to  $y = (x+1)/2 = 0.3 \in [0,1]$ , then encoded into P(Y = 1) = 00101010. The multiplications for

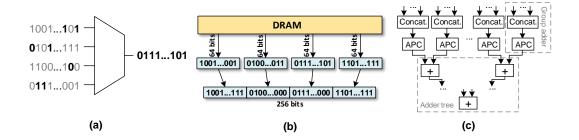

bipolar SC numbers are implemented using XNOR gates (Figure 7(b)). For both unipolar and bipolar formats, additions are commonly calculated by multiplexers (MUXes), as shown in Figure 7(c). A third bit stream Z is required. P(Z=1) is set to a constant 0.5 to give the same probability to select a bit from either A or B. So, the result is a scaled version of addition:  $P(C) = P(Z)P(A) + (1 - P(Z))P(B) = \frac{1}{2}(P(A) + P(B))$ . However, since half of the information in the input bit streams are lost, MUX based addition suffers accuracy reduction. Another way to perform additions more accurately is to use Approximate Parallel Counter (APC). APC counts the number of 1s in input bit streams with some errors to trade off logic gate counts. Figure 7(c) shows an example APC converting a 16-bit SC number to 4-bit binary number. Note that the output of APC is in binary format.

#### 2.5 Related Work

With the prevalence of DNNs, many threats have emerged to DNN security. Accordingly, there are abundant defenses proposed in the literature to tackle those security issues. In this thesis, we classify these works into three categories based on which part of the DNN is the victim: algorithm validity, user privacy, and weight confidentiality. In this section, we present the most influential works that use architectural approaches for defenses.

#### 2.5.1 Algorithm Validity

Attacks that target DNN's algorithm validity attempt to fool the DNNs with deceptive data. For example, adversaries may inject some noises into the input image to make it imperceptible to human beings, resulting in wrong outputs from the DNN. Szegedy et al. [70] is the first literature that found this phenomenon. Most of the attack and defense research fall in this category.

Wang et al. [74] proposes a heterogeneous architecture that couples a DNN accelerator with a CPU core to effectively detect adversary sample attacks. In addition to executing the original DNN task, the proposed architecture also simultaneously runs the detection

algorithm. Guesmi et al. [26] proposes to use hardware-supported approximation as a defense strategy against adversarial attacks. They show that successful adversarial attacks have poor transferability to the approximate DNN implementation. The approximation is introduced by their approximate floating point multiplier, which also results in a significant reduction in power and delay. Fu et al. [24] proposes a precision-scalable accelerator that can randomly quantize the DNN into a different bit width to defend against adversarial attacks. The quantized DNN requires much cheaper computation in accelerators, thus more suitable in resource constraint settings such as Internet of Things (IoT) devices.

# 2.5.2 User Privacy

With advances in DNN architectures, it is becoming harder to train the DNNs. This is because of the massive number of weights, which make the DNNs much more expressive than the patterns present in the training data. It needs a great number of effort to prepare a sufficiently large dataset. For example, data are usually collected and preprocessed by a third party organization. Therefore, the collected data may contain commercial license restrictions or user privacy issues.

The most straightforward protection way is to use encryptions on the input data. However, instead of conventional encryption methods, Homomorphic Encryption (HE) is used to support computing on the encrypted data directly. However, HE introduces thousands of times computation overheads compared to raw data computing. Therefore, a lot of works have been proposed to design DNN accelerators that incorporate hardware HE supports [28, 23, 60]. To avoid the computation overhead of HE, Hashemi et al. [30] proposes to employ the trusted execution environments (TEE) for input privacy and computation integrity verification. Instead of purely relying on hardware to provide privacy guarantees, Mireshghallah et al. [53] propose to fine-tune the pretrained weights to make the DNN learn a special noise distribution which is injected in the input prior feeding to the DNN. The inputs are protected by the noise, while the DNN can still perform normal classification tasks on them.

# 2.5.3 Weight Confidentiality

The last category of attacks on DNNs is to stealing the DNN model itself, including the network architecture and the trained weights. Compared to network architecture, which is either widely known to the public or can be inferred by architectural hints [33], leaking the trained weights is more problematic as it directly relates to the previous two types of security issues. Firstly, knowing the DNN weights makes finding the adversarial samples easier by using gradient based methods [52, 11] (also known as white box attacks as opposed to black box attacks where the adversaries can only access the inputs and outputs of the DNNs). Secondly, it is possible to extract training data information from the trained weights [12], thus leaking the privacy of the training dataset.